三星声称他们正在对基于16Gbit DRAM芯片的256GByte RDIMM取样,为带Xilinx嵌入式FPGA的固态硬盘做好准备。7nm是这次通告的亮点,标志着EUV掩模检测系统内部开发的一次里程碑式的进展。

与10nm节点相比,7LPP工艺可以减少40%的面积同时提高20%的速度,或降低50%的功耗。另外,三星表示他们拥有包括Ansys、Arm、Cadence(具备7nm的数字与模拟流程)、Mentor、Synopsys和VeriSilicon在内的50个Foundry代工伙伴,已经试产出7mn工艺的芯片。

据说这一工艺吸引了众多网站巨头、网络公司以及手机厂商的客户,不过,三星预计在明年初之前不会向客户推送公告。

三星Foundry市场总监Bob Stear指出,自今年初以来,位于韩国华城的Fab工厂S3产线的EUV系统能持续支持250-W光源,这个功率水平使生产量满足了需求量,即1,500个晶片/天。此后,EUV系统达到了280 W的峰值,而三星的目标是300W。

EUV技术使传统氟化氩系统所需的掩模数量减少了五分之一,从而提高了芯片产量。不过,节点在前段制程的基础层中仍需要进行一些多重曝光。

为了加速EUV投入到生产,三星开发了自己的系统来比较和修复预期和实际的掩模曝光。VLSI研究员G. Dan Hutcheson将这个系统描述成一个掩模检查系统,因为目前尚不清楚它是否像典型的第三方检测系统那样自动化。

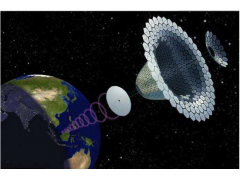

7nm节点将在年底达到Grade 1 AEC-Q100汽车标准。在封装方面,三星正在研发一款RDL插入器,能将多达8个HBM堆叠安装在一个设备上,同时,三星还在开发一种将无源器件嵌入基板的工艺,为了给数据中心的芯片节省出空间。